# THE MEMORIZATION BEHAVIORS OF DIFFERENT MIOS STRUCTURES

# W. F. MOHAMAD L. S. ALI ELECTRICAL ENGINEERING DEPARTMENT COLLEGE OF ENGINEERING UNIVERSITY OF MOSUL

ABSTRACT: In this chapter the various kinds of charge storage cells are discussed as a result of examining many samples with different structures. The C-V, I-V and R-V measurements of the structures confirm the memorization capability of MIOS devices. The examined structures reveal three kinds of memory actions. The first one is the charge storage capability which can be shown through (C-V) curve shifting as the device was exposed to certain stress for a certain time. The second is the electronic switching that is demonstrated by the fact that the switching between ON and OFF states and back to original state can only be obtained by inverting the polarity of the applied bias voltage. The third kind of memorization action is that the device can be switched into a variety of stable intermediate resistance states. The new resistance state is determined by the height of the programming pulse applied to the device. This memory action is noticed from R-V characteristic and known as a nonvolatile analogue memory behavior.

MIOS

# **1-INTRODUCTION**

Essentially the memory devices are structures whose resistance and capacitance vary with magnitude and polarity of applied voltages [1]. The storage devices may be volatile or nonvolatile. They can be used as an analogue or digital memories. The MOS structure is an important type of the memory devices. Recently the shunt capacitance and shunt conductance of such structures have been studied and investigated thoroughly [2,3]. The retention and endurance of charges in the non-volatile memories depend on the oxide layer of the device. The oxide layer is the most important part in the MOS structure. This layer limits the type of the storage device. It is known that the leakage current is responsible for enhanced charge loss in flash EEPROM memory. The leakage current is a tunneling process via neutral traps. The leakage current induced by Fowler-Nordheim (FN) stress in MOS capacitors increases drastically when the oxide thickness decreases [2,3]. The MOS device is essential structure in flash EEPROM memory. It is more important to study the factors and parameters which influence switching and retention of memorization in MIOS structures.

#### **2- MIOS DEVICE FABRICATION**

The MIOS devices used in the present investigation were fabricated as follows:

After the wet chemical treatment of the silicon wafers have been carried out, thermal oxides were grown thermally at 800 °C in dry oxygen for time intervals 15 mins, 25 mins and 35 mins that yield silicon dioxide of thicknesses 7.75 nm, 15.5 nm and 21.7 nm respectively. The oxide thickness tox was calculated from C-V measurement realized at 100 KHz. We are aware that this method gives a rough estimation of the oxide thickness, but for this work we do not need a precise measurement of oxide thickness. The wet chemical treatment was repeated for cleaning only the back sides of all silicon wafers after thermal silicon dioxide (SiO<sub>2</sub>)th growth. Then aluminum was thermally vacuum evaporated on the back side of all wafers as a back contact with thickness of 200 nm. Post-metallization annealing was carried out under vacuum for 60 mins at 400 °C, for making a good ohmic contact between silicon and aluminum as a back contact. Then thermal vacuum evaporated (SiO)<sub>d</sub> film of 100 nm thickness was deposited with a rate of 0.2 nm/sec on a part of the thermal grown silicon dioxide (SiO<sub>2</sub>)<sub>th</sub> using a suitable mask to form (SiO)<sub>d</sub> 100 nm second insulator layer.For other samples the second insulator layer was fabricated by thermal vacuum evaporated  $(SiO_{2})_{d}$ films of 100 nm thickness with deposition rate of 0.2 nm/sec on the thermal grown silicon dioxide (SiO<sub>2</sub>)<sub>th</sub> to form (SiO<sub>2</sub>)<sub>d</sub> 100 nm.For each kind of the MIOS devices, two types of gate contacts were fabricated. For some devices a strip of NiCr of 40 nm was deposited with a rate of 0.2 nm/sec on the second insulator layer using a suitable metallic mask with an aperture of 2 mm width and 20 mm length. In the last step, for all devices, aluminum gate contacts of 200

nm thick were thermally vacuum deposited through the metallic mask with (1 and 2 mm) diameter holes.

# **3- MIOS CHARGE STORAGE CAPABILITY**

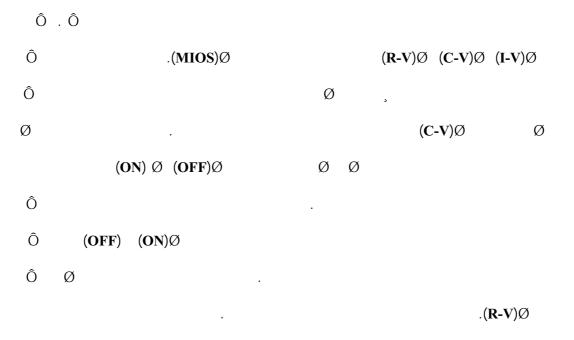

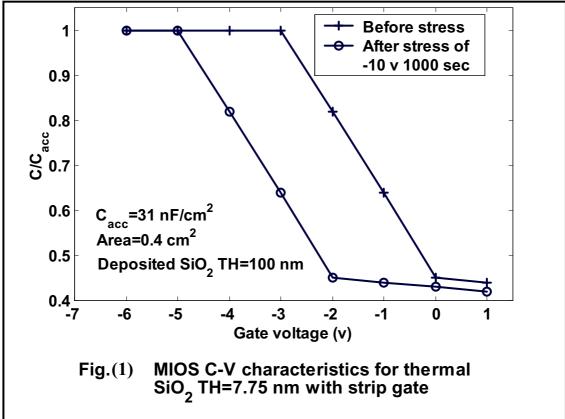

For the MIOS (Al/(SiO<sub>2</sub>)<sub>d</sub>100 nm/(SiO<sub>2</sub>)<sub>th</sub>7.75 nm/p-Si) structure the high frequency (1 MHz) capacitance voltage (C-V) curves were measured before and after stress voltage to evaluate the effect of the stress on the capacitors as shown in Figs.(1) and (2). From the high frequency C-V curves, the characteristics of the flat-band voltage shifts were obtained. The distribution of the generate dinterface-statesdensities were calculated. Before stressing, oxide charges are found to be  $1.63 \times 10^{11}$  charge / cm<sup>2</sup>. After the stress of – 10 V for 1000 sec, the C-V curve indicates the presence of the positive charge in the dioxide. The change in oxide charges are calculated after the stress and are found to be equal to  $\Delta V_{FB} \times C_{acc}$ , i.e. ( $2.6 \times 10^{11}$  charge/cm<sup>2</sup>). That occurred because of tunneling of holes from p-type silicon substrate into the gate structure [4]. Comparing the two C-V characteristics for strip gate and dot gate samples, it is clear that the shift window in the dot gate sample approaches 2.5 V while in the strip gate sample is about 2 V. This is attributed to the more tunneling back of holes near Si/SiO<sub>2</sub> interface into Si substrate in the strip gate sample after removing a stress voltage because of larger area and larger defects. Hence, the density of remained store charges will be less [5].

# 4- MIOS DIGITAL PROGRAMMABLE RESISTOR MEMORY

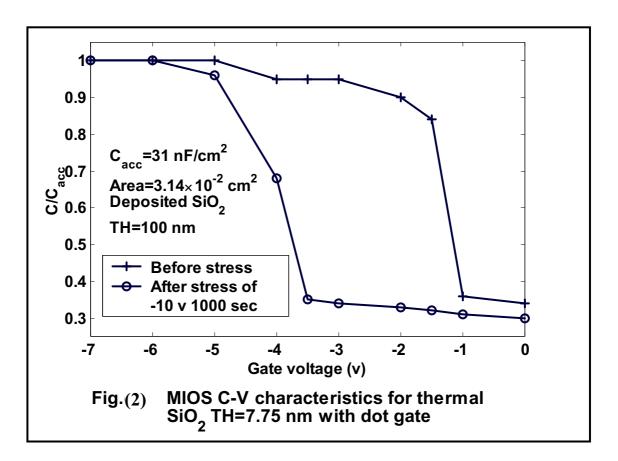

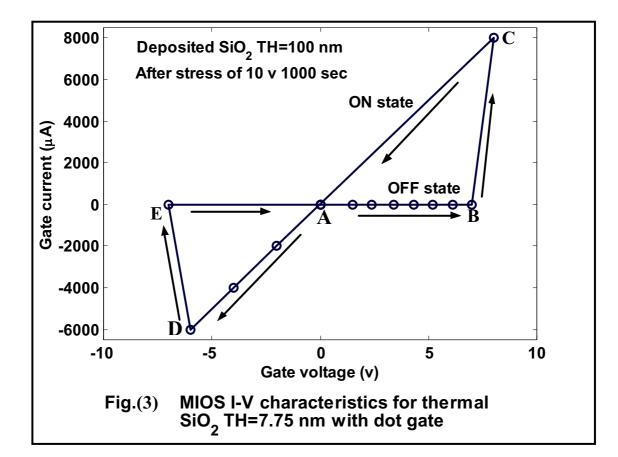

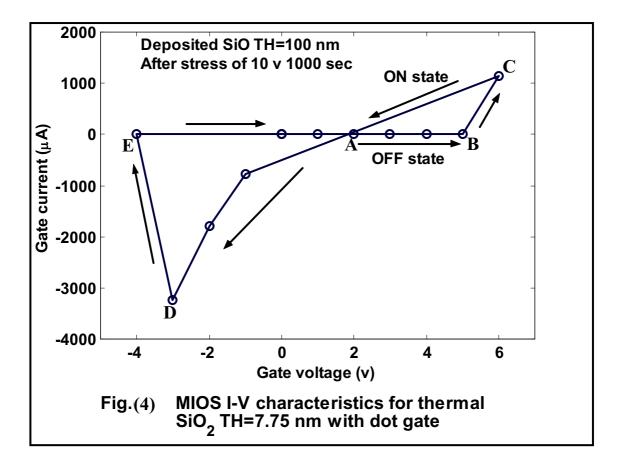

Switching action of the two kinds of devices has been studied after exposing them to a stress voltage of 10 V for 1000 sec. The experimental I-V curves for each device in "OFF" and "ON" states are illustrated in Figs.(3) and (4). It is clear from both figures that these devices exhibit memory switching [6]. Both the ON-state and the OFF-state characteristics extrapolate through the I-V origin. The on-state is thus retained once the bias is removed, giving a non-volatile, memory switching. By applying a negative bias the device can be switched from conducting ON-state back to the OFF-state. From the two characteristics shown, the behavior of each device differs from the other. The switching voltage from the OFF-state (line AB) to ON-state (line CAD) for the device of SiO deposited insulator is between (5-6) V, while that for SiO<sub>2</sub> deposited insulator is between (7-8) V. In the reverse direction the switching voltage from the ON-state (line CAD) to the OFF-state (line EA) for the device of SiO deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -3V and -4V, while that for SiO<sub>2</sub> deposited insulator is between -6V and -7V.

The two devices are of the same thermal tunnel silicon dioxide of 7.75 nm thickness. The difference in the switching voltages is attributed to the second deposited insulator difference, because both deposited insulators (SiO and SiO<sub>2</sub>) have the same thickness (100 nm). The forming effect in SiO deposited layer happens at a voltage less than that of  $SiO_2$  deposited layer, i.e. the insulation reliability of SiO is less than that of  $SiO_2$

[7]. Although the programming mechanism of this memory device is not yet understood fully [1], it is thought that the current in a formed device is carried by a filament which is less than 1  $\mu$ m in diameter. Formation of a filament may be associated with a diffusion of the top metal into the insulator layer, resulting in a dispersion of metallic atoms in the insulating (SiO and SiO<sub>2</sub>) matrix [8].

# **5- MIOS ANALOGUE PROGRAMABLE RESISTOR MEMORY**

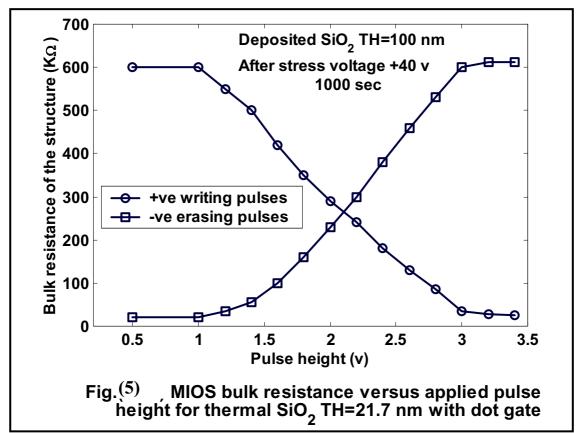

Non-volatile memory switching has been observed in

$Al/(SiO_2)_d$  100 nm/(SiO\_2)<sub>th</sub> 21.7 nm/(p-Si) (MIOS) structure. Evidence for filamentary conduction is found for devices that are in their low impedance state. The switching phenomenon requires the existence of two impedance states which are stable at zero applied bias. The device tested showed memory switching and their initial state was one of high resistance. Fig.(5) shows analogue switching characteristic of  $Al/(SiO_2)_d$  100 nm/(SiO<sub>2</sub>)<sub>th</sub> 21.7 nm/(n-Si) (MIOS) device.

After the device was exposed to stress voltage of 40 V for 1000 sec., the device displayed a non-volatile, analogue memory behavior. The resistance state is determined by the height of the programming pulse applied to the device. The range of programming voltages that can be applied is referred to as the programming window. The operation of the device involves the following processes [1]:

<sup>1.</sup> Forming: This is an only one time process in which a stress of 40 V for 1000 sec is applied across the device electrodes. This creates a vertical deep conducting channel of submicron width, which can be programmed to a value in the range 500  $\Omega$  to 600 K $\Omega$ .

- 2. Writing: To decrease the device resistance, positive "write" pulses are applied.

- 3. Erasing: To increase the device resistance, negative "erase" pulses are applied.

- 4. The device resistance can be "read" using a voltage of less than 0.2 V without causing reprogramming.

The programming pulses (write or erase), which range between 1 V and 3 V, are typically 500 nsec width. In Fig.(5) the device resistance is seen to increase from 500  $\Omega$  toward 600 K $\Omega$  depending on the height

of the erase negative pulse. The magnitude of write positive pulse is used to set the final resistance of the device. The programming window is 2 V.

It is thought [9] that the current in a formed device is carried by a filament, which is less than 1  $\mu$ m in diameter. Formation of a filament may be associated with a diffusion of the top metal into the amorphous SiO<sub>2</sub> layers, resulting in a dispersion of metallic atoms in the insulating

$SiO_2$  matrix [10]. At Si-SiO\_2 interface, when the device is in the high resistance state, it is characterized by a large device voltage and low device current. In this state the semiconductor under the tunnel oxide is deep depleted since any minority charge at Si-SiO<sub>2</sub> interface is effectively drained away by the tunnel-oxide. At switching point the device becomes unstable due to the initiation of a regenerative feedback mechanism [3], which collapses the width of the deep-depletion region to its strong-inversion value.

#### **6- CONCLUSIONS**

The examined devices manifest three kinds of memorization phenomena. The first one is the charge storage capability which can be noticed through C-V curve displacement when stressing the device. The second is the digital memory switching which is demonstrated by the fact that the switching between ON and OFF states and back can only be obtained by inverting the polarity of applied bias voltage. The third kind of memorization noticed in this work is that a device can be switched into a variety of stable intermediate resistance states. The new resistance states could be determined by the height of the programming applied pulses. This phenomenon is known as the analogue memorization.

### **7- REFERENCES**

- [1] A. F. Murray and L. W. Buchan, "A users guide to non-volatile on-chip analogue memory", Electronics & Communication Engineering Journal PP. 53-63, April, 1998.

- [2] P. L. Swart and C. K. Cmpbell, "Effect of losses and parasitic on a voltage-controlled tunable distributed RC notch filter" IEEE J. Solid-State Circuits, Vol. SC-8, No. 1, PP. 35-36, 1973.

- [3] J. G. Simmons, L. Faraone, U. K. Mishra, and F. L. Hsueh, "Determination of the switching criterion for metal/tunnel oxide/n/ p+ silicon switching devices", IEEE Electron Device Letters, Vol. EDL-2, No. 5, PP. 109-112, 1981.

- [4] A. Meinertzhgen, C. Petit, M. Jourdain, and F. Mondon, "Anode hole injection and stress induced leakage current decay in metal-oxide-semiconductor capacitors", Solid-State Electronics Vol. 44, PP. 623-630, 2000.

- [5] T. Y. Huang and W. W. grannemann, "Non-volatile memory properties of metal / SrTiO<sub>3</sub> / SiO<sub>2</sub> / Si structures", Thin Solid Films, 87, PP. 159-165, 1982.

- [6] J. M. Shannon and S. P. Lau, "Memory switching in amorphous silicon-rich silicon carbide", Electronics Letters Vol. 35, No. 22, PP. 1976-1977, 1999.

- [7] H. F. Wolf "Semiconductors" Copy right 1971, by John Wiley & Sons, Inc.

- [8] G. Dearnaley, D. V. Morgan, and A. M. Stoneham, "A model for filament growth and switching in amorphous oxide films", J. Non-Crystalline Solids 4, PP. 593-612, 1970.

- [9] H. Kroger and H. A. Ricahrd Wegener, "Memory switching in polycrystalline silicon films", Thin Solid Films, 66, PP. 171-176,

1980.

[10] D. V. Morgan, A. E. Guile and Y. Bektore, "Switching times and arc cathode emitting site life-times for aluminum oxide films", Thin Solid Films, 66, PP. L 35-L 38, 1980.