# **Engineering and Technology Journal**

Journal homepage: engtechjournal.org

## Study of Power System Load Flow Using FPGA and LabVIEW

Ahmed Y. Yaseen @a\*, Afaneen A. Abboodb

- <sup>a</sup> Southern Technical University, Nasiriyah, Iraq, <u>ahmedyahya@stu.edu.iq</u>

- <sup>b</sup> University of Technology, Baghdad, Iraq, afaneenalkhazragy@yahoo.com

\*Corresponding author.

Submitted: 11/6/2019 Accepted: 31/8/2019 Published: 25/05/2020

#### KEYWORDS

#### ABSTRACT

power flow, FPGA, LabVIEW, monitoring system

The capability to rapidly execute the power flow (PF) calculations permit engineers in assured with stay bigger assured within the dependability, protection, and economical operation of their system within the case of planned or unplanned instrumentality failures. The purpose of this work is to investigate the use of FPGA characteristics to speed up power flow computing time for the on-line monitoring system of a power system. The work comprises which is the development of the Power flow program using the Fast-decoupled method based on FPGA (Field Programmable Gate Array), and LABVIEW (graphical programming environment). The program delivered very satisfactory results to solve a 30-bus test system. These findings suggest that in general that differences between the proposed work and the conventional fast decoupled method are satisfactory. As for the execution time, because the FPGA uses parallel solutions, the performance of the proposed method is faster. Also, the engagement of the FPGA and the LabVIEW program presented an effective monitoring system for observing the power system.

**How to cite this article**: Ahmed Y. Yaseen, Afaneen A. Abbood, "Study of power system load flow using FPGA and labVIEW," *Engineering and Technology Journal*, Vol. 37, Part A, No. 05, pp. 690-697, 2019. DOI: <a href="https://doi.org/10.30684/etj.v38i5A.346">https://doi.org/10.30684/etj.v38i5A.346</a>

This is an open access article under the CC BY 4.0 license http://creativecommons.org/licenses/by/4.0.

#### 1. Introduction

Calculations of power flow are a foundation on which most analyses of the electrical system are based. The power flow calculation results are used to estimate a power system operation under a group, of known cases. The systems are certainly not static and one of the many input cases can be modulated[1]. When the power flow problem is solved for the given operating conditions, we can specify the voltage value and the phase angle  $\delta$  in each power system bus, which will determine the active and reactive power values in each line. The power injected at each node can be determined, which gives us the value of the active and reactive power loss of the power system[2]. The techniques for solving load flow rely on the iterative solution of the power flow equation such as

Gauss-sidle(GS), Newton-Raphson(NR) and fast decoupled methods. There are many studies dealt with load flow analysis using various techniques[3][4][5][6]

In power system analysis, many applications are using the FPGA board.in [7], [8], to study electromagnetic transient switching in 3-phase AC machines and power converters for the real-time digital simulator. Also, use the FPGA to analyze the power grid frequency and harmonics signal based on the all-phase FFT spectrum theory. This work used the FPGA (myRIO FPGA) technology to solve the problem of load flow based on the fast decoupled method of LabVIEW's graphical programming environment.

## 2. The Fast-Decoupled Load Flow(FDLF) method

The fast decoupled method is an (NR) modulation that takes advantage of weakly conjugation between  $P - \delta$  and Q - V due to high X:R ratios[3]. The numerical analysis included in computeraided electrical energy system analysis is founded on the solution of algebraic equations for execution equations. The first task in the calculation of Power Flow (PF) is to use input data from the transformer and transmission line (TL) to form Y<sub>bus</sub>. The nodal equations for a Y<sub>bus</sub> power system can be written as follows [9]:

$$I = YV \tag{1}$$

The nodal equation of the n-bus system may be written in a general form:

$$I_i = \sum_{j=1}^n Y_{ij} * V_j$$

for  $I = 1,2,3$ , ...,n (2)

power supplied to I bus: The complex

$$P_{i} + j Q_{i} = V_{i} * I_{i}^{*}$$

(3)

$$I_i = \frac{P_i - J Q_i}{V_i^*} \tag{4}$$

$P_{i} + j Q_{i} = V_{i} * I_{i}^{*}$   $I_{i} = \frac{P_{i} - j Q_{i}}{V_{i}^{*}}$ By substituting I in terms Pi and Qi the equation gives:

$$\frac{P_i - jQ_i}{V_i^*} = V_i \quad \sum_{j=1}^n y_{ij} - \sum_{j=1}^n y_{ij} \quad V_j \quad j \neq i \quad (5)$$

Equation (2) is written in the polar form in which j includes bus i:

$$I_i = \sum_{j=1}^n |Y_{ij}| |V_i| \angle (\theta_{ij} + \delta_j) \tag{6}$$

Active and Reactive power at the bas I is:

$$P_i - jQ_i = V_i^* I_i$$

in Equation (6) from Equation (7):

By substituting Ii

$$P_{i} - jQ_{i} = |V_{i}| \angle (-\delta_{i}) \sum_{j=1}^{n} |Y_{ij}| |V_{j}| \angle (\delta_{ij} + \delta_{j})$$

(8)

Separate the actual parts from the imaginary:

$$P_{i} = \sum_{j=1}^{n} |V_{i}| |V_{j}| |Y_{ij}| \cos(\theta_{ij} - \delta_{i} + \delta_{j})$$

$$(9)$$

$$Q_i = -\sum_{j=1}^{n} |V_i| |V_j| |Y_{ij}| \sin(\theta_{ij} - \delta_i + \delta_j)$$

(10)

Equation (9) and (10) are a collection of algebraic un-linear equations in terms of voltage magnitude per unit and angle in radians. In Taylor's initial estimate series, equation (9) and (10) develop and the following linear formulas are obtained neglecting all higher-order terms[10].

$$\begin{bmatrix} \Delta P_{2}^{(K)} \\ \vdots \\ \Delta P_{n}^{(K)} \\ \vdots \\ \Delta Q_{n}^{(K)} \end{bmatrix} = \begin{bmatrix} \frac{\partial P_{2}^{(k)}}{\partial \delta_{2}} & ... & \frac{\partial P_{2}^{(k)}}{\partial \delta_{n}} \\ \vdots & \ddots & \vdots \\ \frac{\partial P_{n}^{(k)}}{\partial \delta_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial \delta_{n}} \\ \frac{\partial P_{n}^{(k)}}{\partial \delta_{n}} & ... & \frac{\partial P_{n}^{(k)}}{\partial \delta_{n}} \\ \frac{\partial P_{n}^{(k)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial V_{n}} \end{bmatrix} \begin{bmatrix} \Delta S_{2}^{(K)} \\ \vdots \\ \Delta S_{n}^{(K)} \\ \frac{\partial P_{n}^{(k)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial V_{2}} \\ \frac{\partial P_{n}^{(k)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial V_{2}} \end{bmatrix} \begin{bmatrix} \Delta S_{2}^{(K)} \\ \vdots \\ \Delta S_{n}^{(K)} \\ \frac{\partial P_{n}^{(K)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial V_{2}} \\ \frac{\partial P_{n}^{(k)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(k)}}{\partial V_{n}} \end{bmatrix} \begin{bmatrix} \Delta S_{2}^{(K)} \\ \vdots \\ \Delta V_{n}^{(K)} \\ \frac{\partial P_{n}^{(K)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(K)}}{\partial V_{2}} \\ \frac{\partial P_{n}^{(K)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(K)}}{\partial V_{2}} \\ \frac{\partial P_{n}^{(K)}}{\partial V_{2}} & ... & \frac{\partial P_{n}^{(K)}}{\partial V_{2}} \end{bmatrix} \begin{bmatrix} \Delta S_{2}^{(K)} \\ \vdots \\ \Delta V_{n}^{(K)} \end{bmatrix}$$

Since they are already known, the swing(slack) bus voltage |V| & angle  $\delta$  is neglected. Jacobian components are obtained after partial equations (9) & (10) derivatives. The equation is written in the form of a matrix:

$$\begin{bmatrix} \Delta P \\ \Delta Q \end{bmatrix} = \begin{bmatrix} J_1 & J_3 \\ J_2 & J_4 \end{bmatrix} \begin{bmatrix} \Delta & \delta \\ \Delta | V | \end{bmatrix} \tag{11}$$

$\begin{bmatrix} \Delta P \\ \Delta Q \end{bmatrix} = \begin{bmatrix} J_1 & J_3 \\ J_2 & J_4 \end{bmatrix} \begin{bmatrix} \Delta & \delta \\ \Delta | & V | \end{bmatrix} \tag{11}$   $J_1, J_2, J_3, \text{ and } J_4 \text{ are Jacobian matrix components. The variances between the specific values and the calculated values for the terms <math>\Delta P_i^{(k)}$  and  $\Delta Q_i^{(k)}$  are called power residuals and are represented as:

$$\Delta P_{i}^{(k)} = P_{i}^{(sch)} - P_{i}^{(k)}$$

(12)

(13)

The new bus

S:

$$\Delta P_{i}^{(k)} = P_{i}^{(sch)} - P_{i}^{(k)}$$

(12)

$$\Delta Q_{i}^{(k)} = Q_{i}^{(sch)} - Q_{i}^{(k)}$$

(13) voltage values are:

$$\delta_{i}^{(k+1)} = \delta_{i}^{(k)} + \Delta \delta_{i}^{(k)}$$

(14)

$$|V_{i}^{(k+1)}| = |V_{i}^{(k)}| + \Delta |V_{i}^{(k)}|$$

(15)

Each iteration has to recalculate the Jacobian matrix terms and the linear equations set in Equation (11). As the planning or operating study usually performs thousands of power flow analyses, Finding ways to accelerate this process was important[11]. The equation's Jacobian matrix (11) is minimized to half due to the negligence of J 2 and J 3 element:

$$\begin{bmatrix} \Delta P \\ \Delta Q \end{bmatrix} = \begin{bmatrix} J_1 & 0 \\ 0 & J_4 \end{bmatrix} \begin{bmatrix} \Delta \delta \\ \Delta |V| \end{bmatrix}$$

Expanding Equation (16) has two different matrixes :

on (16) has two different matrixes

$$\Delta P = J_1 \ \Delta \delta = \left[ \frac{\partial P}{\partial \delta} \right] \Delta \delta \qquad (17)$$

$$\Delta Q = J_4 \ \Delta |V| = \left[ \frac{\partial Q}{\partial |V|} \right] \ \Delta |V| \qquad (18)$$

$$\frac{\Delta P}{V_i} = -B' \ \Delta \delta \qquad (19)$$

$$\frac{\Delta Q}{V_i} = -B'' \ \Delta |V| \qquad (20)$$

B '& B " are bus admittance's imaginary components. Ignoring all connected shunt parts is higher, making  $J_1$  and  $J_4$  easier to form. This can only allow one matrix to perform a repetitive inversion. Successive changes in voltage |V| and angle  $\delta$  are:

$$\Delta \delta = -\left[B'\right]^{-1} \frac{\Delta P}{|V|} \tag{21}$$

$$\Delta \delta = - [B']^{-1} \frac{\Delta P}{|V|}$$

$$\Delta |V| = - [B'']^{-1} \frac{\Delta Q}{|V|}$$

(21)

#### 3. The FPGA architecture

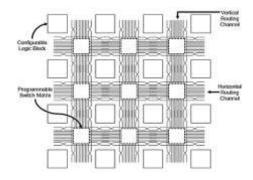

The Field Programmable Gate Array (FPGA) is an array of configurable logic blocks (CLBs) linked through a programmable interconnection network and configurable inputs/outputs [12]. The sum of these parts forms the basic reconfigurable fabric of an FPGA, illustrated in Figure (1). Since the same manufacturing technologies used to make integrated circuits are also used to manufacture FPGAs, FPGAs benefit from a periodic doubling of device density as predicted by Moore's Law. FPGA designers have used these increased resources not only for additional reprogrammable logic but have also expanded CLB functionality, and incorporated high performance fixed function blocks such as binary multipliers, embedded memory blocks, high-speed programmable input/output devices, and fully functional microprocessors into the reconfigurable fabric[13].

Figure 1: The FPGA Architecture [14]

## 4. Structure of the proposed program

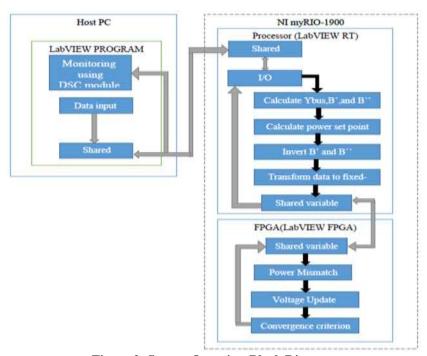

The work contains two parts to build the main system as shown in figure (2). The structure of the load flow analysis and the monitoring program, the parts are summarized as follows:

## Part one which contains:

- **1.** Reading the line and bus data (Input data).

- 2. Sending the input data from the host PC using a shared variable to NI-myRIO.

- **3.** based on the figure (3) the work will be divided inside the hardware to:

- A- A Processor (LabVIEW RT)

- Calculate Y<sub>bus</sub>, B', and B''.

- Invert B' and B".

- Calculate the power set point.

- Transform data to fixed-point.

- Send this data to FPGA (LabVIEW FPGA) using a shared variable.

- FPGA (LabVIEW FPGA)

- Calculating the Power Mismatch using equations (12) and (13).

- Updating the voltage using equations (14), (15), (21), and (22).

- Checking the convergence criterion.

- Sending the results back to I/O MEMORY table in LabVIEW RT part using the shared variable.

- Sending the results to the HOST PC.

## Part two which contains

Displaying the results on the screen using the DSC module (Data-logging and Supervisory Control Module).

Figure 2: System Overview Block Diagram

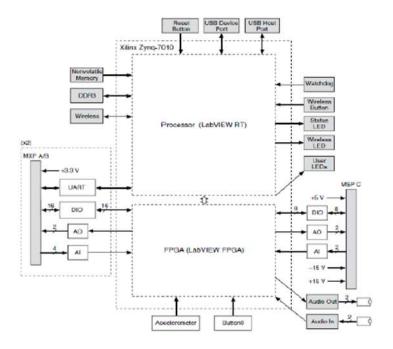

Figure 3: NI myRIO-1900 hardware block diagram

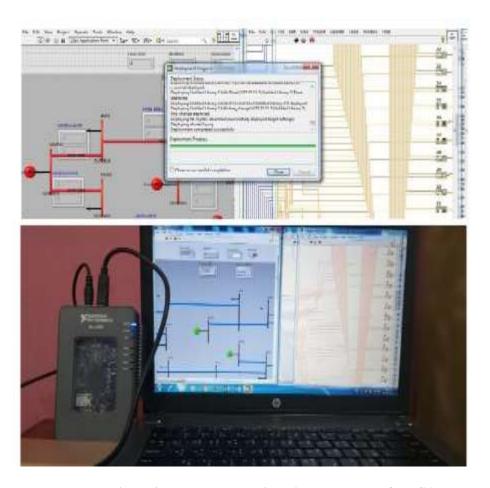

The practical aspect of the job includes connecting a personal laptop with the operating system Windows 7 Home Premium, which was configured with the required assistance from LabVIEW. The PC is also used as a monitoring application screen terminal. Figure (4) is the main program connection to the FPGA NI-myRIO.

Figure 4: program connection with the NI-myRIO FPGA

#### 5.Case study

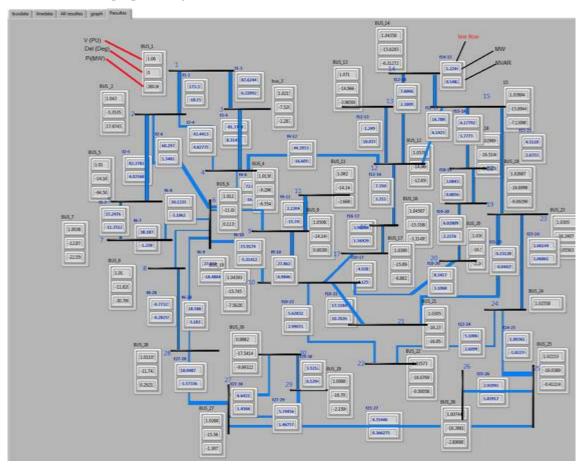

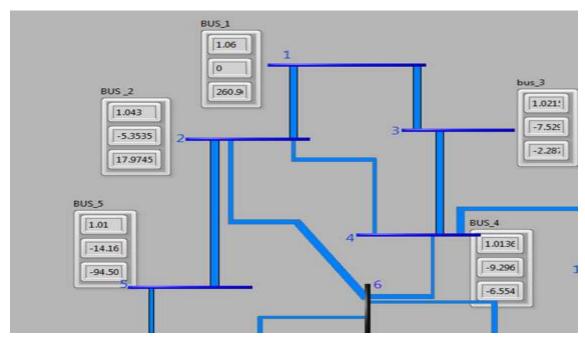

To verifying the effectiveness of the proposed program, it was applied to the IEEE 30-bus test system. All its data are illustrated in the appendix. Figure (5) shows the results of the network built within the program. The program can show the information of any busbar after clicking it as shown in Figure (6). The findings of this study were compared to the findings of reference[15] for the analysis of power flow calculation and were identical. On the other hand, the execution time of the proposed algorithm was compared with a built power flow program using the conventional fast decoupled method and was applied to the test system. The results show that the proposed program execution time was 0.0362191 sec and the conventional MATLAB program execution time was 0.097886 sec. Therefore, the reduction of the execution time was 63%. Which shows the effectiveness of the proposed algorithm.

Figure 5: The IEEE 30 Busbar network is drawing in the program as SCADA

Figure 6: The result when clicking on the busbar (1,2,3,4, and 5)

#### 6. Conclusions

The current study set out to assess the importance of load flow for the power system. This study set out to calculate the load flow based on NI myRIO-1900(FPGA). The program was implemented in the FPGA using the LabVIEW. The current study found that through the application, the program delivered very satisfactory results to solve a test system of 30 buses. These findings suggest that in general that differences between the proposed work and the conventional fast decoupled method are satisfactory. As for the execution time, because the FPGA uses parallel solutions, the performance of the proposed method is faster. Also, the engagement of the FPGA and the LabVIEW program presented an effective monitoring system for observing the power system.

The proposed work produces a prototype implementation of an FPGA based load flow solver in such a way that the hardware design can be connected directly to the electrical system and the load flow can be converted from off-line application to online application.

#### References

- [1] J. Foertsch, J. Johnson, and P. Nagvajara, "Jacobi load flow accelerator using FPGA," Proc. 37th Annu. North Am. Power Symp. 2005, vol. 2005, no. August, pp. 448–454, 2005.

- [2] S. Souag, F. Benhamida, F. Z. Gherbi, and A. Graa, "A new software for power flow solution computing using LabVIEW," 2013 5th Int. Conf. Model. Simul. Appl. Optim. ICMSAO 2013, no. November 2014, 2013.

- [3] I. A. Adejumobi, G. A. Adepoju, K. A. Hamzat and O. R. Oyeniran, "Numerical methods in load flow analysis: an application to the nigerian grid system," International Journal of Electrical and Electronics Engineering, vol. 3, no. 2, pp. 43–52, 2014.

- [4] X. Wang, S. G. Ziavras, C. Nwankpa, J. Johnson, and P. Nagvajara, "Parallel solution of newton's power flow equations on configurable chips," vol. 29, pp. 422–431, 2007.

- [5] S. Kumar, S. Ahmad, and A. Ahmad, "Analysis of load flow study using pso and compensate the system using facts device," vol. 3, no. 6, pp. 6555–6560, 2014.

- [6] S. K. Avakian and A. Alkhazraji, "The Application of Agent Technology on the Power Flow of Iraqi Supper Grid Network," American Journal of Applied Sciences, 3, 12, 2174-2177, 2018

- [7] R. Razzaghi, S. Member, M. Paolone, S. Member, and F. Rachidi, "A general purpose FPGA-based real-time simulator for power systems applications," pp. 1–5, 2013.

- [8] X. Chen and Y. Zhang, "Detection and analysis of power system harmonics based on FPGA," *Lect. Notes Inst. Comput. Sci. Soc. Telecommun. Eng.*, vol. 72 LNICST, pp. 445–454, 2012.

- [9] O. A. Afolabi, W. H. Ali, P. Cofie, J. Fuller, P. Obiomon, and E. S. Kolawole, "Analysis of the Load Flow Problem in Power System Planning Studies," no. September, pp. 509–523, 2015.

- [10] K. Singhal, "Comparison between load flow analysis methods in power system using MATLAB," vol. 5, no. 5, 2014.

- [11] S. Souag and F. Benhamida, "A virtual instrument for DC power flow solution using LabVIEW language," *Adv. Electr. Electron. Eng.*, vol. 10, no. 2, pp. 68–74, 2012.

- [12] I. Kuon, R. Tessier, and J. Rose, FPGA Architecture: Survey and Challenges, vol. 2, no. 2. 2007.

- [13] Xilinx, "Virtex-5 FPGA User Guide," vol. 225, pp. 1–36, 2010.

- [14] "Power flow computation using field programmable gate arrays," no. June, 2007.

- [15] H. Saadat, "Power system analysis," Hadi Saadat.pdf. 1999.